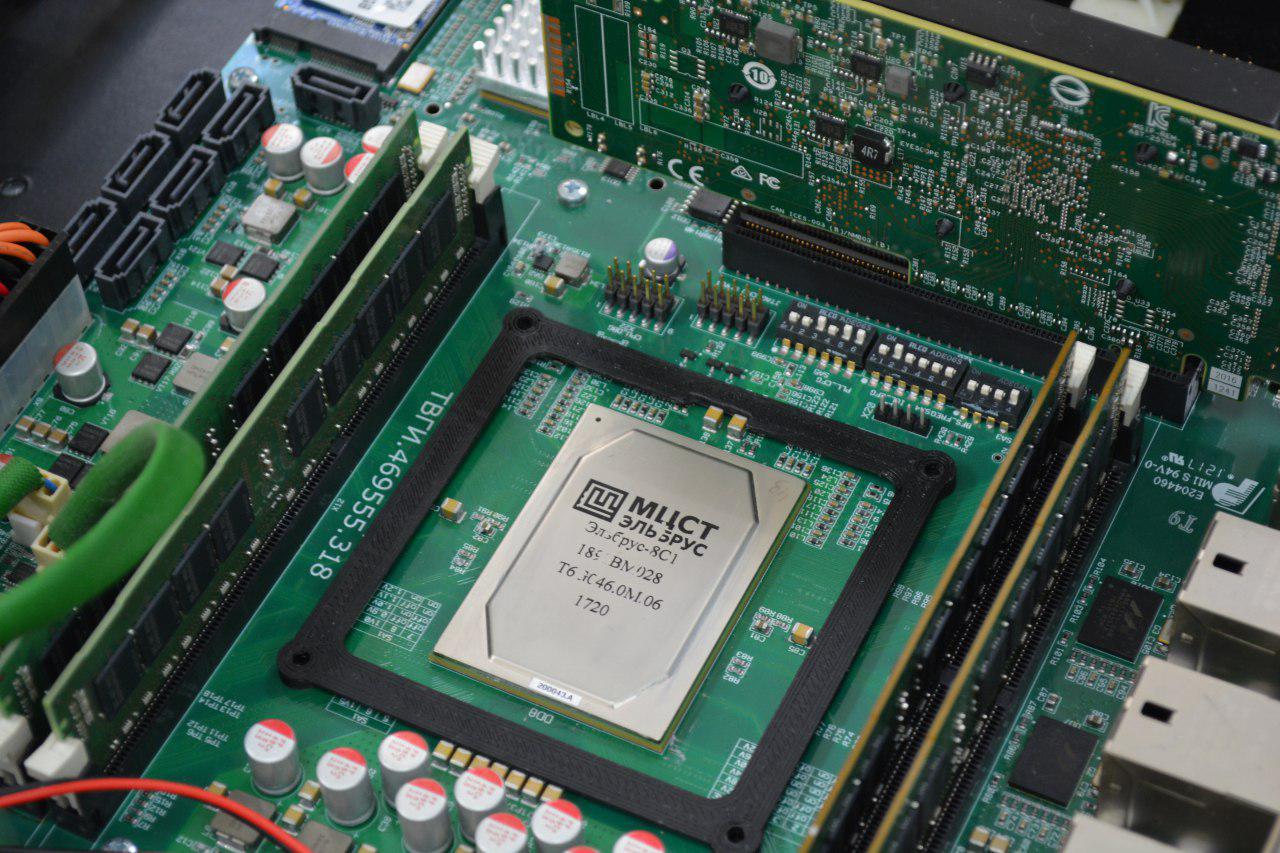

Описание

«Эльбрус» — процессорная архитектура и одноимённое семейство универсальных VLIW-микропроцессоров, разрабатываемых российской компанией МЦСТ при участии ИНЭУМ, продолжая развитие процессорных технологий советских вычислительных комплексов «Эльбрус». Наименование «Elbrus» — акроним от англ. ExpLicit Basic Resources Utilization Scheduling — «явное планирование использования основных ресурсов».

Основные особенности

- Широкая команда, способная при максимальном заполнении задать в одном такте до 23 операций (более 33 операций при упаковке операндов в векторные команды)

- Поддержка спекулятивных вычислений и однобитовых предикатов. Позволяет уменьшить число переходов и параллельно исполнять несколько ветвей программы.

- Программируемое асинхронное устройство предварительной подкачки данных с отдельными каналами считывания. Позволяет скрыть задержки от доступа к памяти и полнее использовать АЛУ.

- защищённый режим — аппаратный контроль целостности структуры памяти, обеспечивающий информационную безопасность

- отсутствие микрокода — компилятор переводит исходный код сразу в двоичный код, минуя микрокод, как это реализовано на x86

- Аппаратная поддержка циклов, в том числе с конвейеризацией. Повышает эффективность использования ресурсов процессора

- 6 каналов арифметико-логических устройств (АЛУ), работающих параллельно.

Работа с периферией в процессоре обеспечивается через контроллеры серии КПИ (контролер периферийных устройств) — название серии южных мостов, разработанных компании МЦСТ для компьютеров на процессорах Эльбрус и МЦСТ R. Серия КПИ (2010) предназначена для процессоров 4С, 2СМ, 2С+ и МЦСТ R1000В, серия КПИ-2 — для 8С, 1С+, МЦСТ R1000, в последующих моделях процессора южный мост встроен, однако сохранена возможность подключать дополнительно контроллер КПИ-2 для расширения набора периферии. В связи с ограниченным спросом процессоры «Эльбрус» производят малыми сериями под заказ, используются две площадки — завод Микрон в Зеленограде (техпроцесс до 90 нм) и фабрика TSMC в Синьчжу. В 2017 году планировалось наладить выпуск Эльбрус-4СМ — адаптированную версию Эльбрус-4С под мощности завода «Микрон», но предприятие не смогло перейти на необходимый для этого техпроцесс 65 нм. В отличие от Intel и AMD, МЦСТ находится в роли догоняющего, резко меняя техпроцесс: если в 2014 году Эльбрус-4С производился по технологии 65 нм, то в 2016 году технология выпуска Эльбрус-8С — это 28 нм. Ввиду ограниченности ресурсов, МЦСТ сосредоточено на разработке небольшого количества моделей с периодичностью выпуска в 2—5 лет; прирост производительности в каждом поколении — на уровне 100—500 %. Все выпускаемые процессоры Эльбрус напаиваются на материнскую плату, что делается как для удешевления производства и разработки готовых устройств, так и из-за высокой цены процессора (незначительная доля стоимости материнской платы).

Операционные системы

ОС, поддерживающие процессоры архитектуры «Эльбрус»: QNX (российская сборка ЗОСРВ «Нейтрино-Э» КПДА.10965-01), ОСРВ «БагрОС-4000»[1], также выпущен ряд дистрибутивов Linux — ОС Эльбрус, МСВС, ALT Linux, Astra Linux Special Edition «Ленинград», Лотос[2][3].

Ключевые особенности архитектуры

В традиционных архитектурах типа RISC или CISC (х86, PowerPC, SPARC, MIPS, ARM), на вход процессора поступает поток инструкций, которые рассчитаны на последовательное исполнение. Процессор может детектировать независимые операции и запускать их параллельно (суперскалярность) и даже менять их порядок (внеочередное исполнение). Однако динамический анализ зависимостей и поддержка внеочередного исполнения имеет свои ограничения: лучшие современные процессоры способны анализировать и запускать до 4-х команд за такт. Кроме того, соответствующие блоки внутри процессора потребляют заметное количество энергии. В архитектуре «Эльбрус» основную работу по анализу зависимостей и оптимизации порядка операций берет на себя компилятор. Процессору на вход поступают т.н. «широкие команды», в каждой из которых закодированы инструкции для всех исполнительных устройств процессора, которые должны быть запущены на данном такте. От процессора не требуется анализировать зависимости между операндами или переставлять операции между широкими командами: все это делает компилятор, исходя из анализа исходного кода и планирования ресурсов процессора. В результате аппаратура процессора может быть проще и экономичнее. Компилятор способен анализировать исходный код гораздо тщательнее, чем аппаратура RISC/CISC процессора, и находить больше независимых операций. Поэтому в архитектуре Эльбрус больше параллельно работающих исполнительных устройств, чем в традиционных архитектурах, и на многих алгоритмах она демонстрирует непревзойденную архитектурную скорость.

Эмуляция архитектуры x86

Еще на этапе проектирования МП Эльбрус у разработчиков было понимание важности поддержки программного обеспечения, написанного для архитектуры Intel х86. Для этого была реализована система динамической (т.е. в процессе исполнения программы, или «на лету») трансляции двоичных кодов х86 в коды процессора Эльбрус. Фактически, система двоичной трансляции создает виртуальную машину, в которой работает гостевая ОС для архитектуры х86. Благодаря нескольким уровням оптимизации удается достичь высокой скорости работы оттранслированного кода (см. диаграммы выше). Качество эмуляции архитектуры х86 подтверждается успешным запуском на платформе Эльбрус более 20 операционных систем (в том числе несколько версий Windows) и сотен приложений.